PXIe FPGA development boards sit at the center of many high-value test and measurement systems — radar signal processing, electronic warfare, satellite data capture, high-speed data recording, and automated test. When a program needs to procure one, replace one, or evaluate competing options, the decision lands on procurement and program managers who need to ask the right questions without necessarily having a background in FPGA architecture.

This guide covers what these boards do, which specifications actually drive cost and performance, what total cost of ownership looks like beyond the purchase price, how to evaluate vendors, and how to manage program risk through the selection process. Engineers will weigh in on the technical fit. Your job is to structure the evaluation and ensure the right questions get asked before a commitment is made.

What a PXIe FPGA Board Is and Why It Matters to Your Program

PXI Express (PXIe) is a modular test and measurement platform. A PXIe chassis is a rack-mounted enclosure that houses a controller and a collection of instrument modules — one per slot. These modules share a common backplane that provides power, synchronized clocking, and trigger signals across all cards in the system. The platform is widely used in defense, aerospace, telecommunications, and research because it enables complex, synchronized multi-instrument systems from a mix of vendor-supplied and custom hardware.

A PXIe FPGA development board puts a user-programmable processing chip — a field-programmable gate array, or FPGA — into one of those chassis slots. The FPGA runs custom logic programmed by your engineering team: signal processing algorithms, data routing, protocol handling, waveform generation, or whatever the application requires. The board connects to the host controller via the chassis backplane and to external instruments or sensors via high-speed serial ports on the front panel.

From a program perspective, the FPGA board is typically a platform on which significant engineering investment sits. The FPGA design — often representing months of development work — runs on a specific board. When that board becomes unavailable, goes end-of-life, or is priced at a level that strains the program budget, the question of replacement or alternative sourcing becomes a program risk item, not just a procurement transaction. Understanding what drives cost, performance, and compatibility in this product category gives you the foundation to structure a sound evaluation.

The Specifications That Drive Price and Performance

PXIe FPGA board datasheets list specifications that can look similar across competing products while representing very different price points and capabilities. These are the specifications that actually drive hardware cost and performance — and what each one means for your program.

FPGA Device and Generation

The FPGA chip is the largest single cost driver in a PXIe FPGA board. Current-generation devices from AMD (formerly Xilinx) cost more than legacy devices, but provide more capability and longer manufacturer support windows. FPGA families evolve in generations — the 7 Series (Kintex 7, Virtex 7) is the previous generation; UltraScale and UltraScale+ are current. A board built around a legacy device may be approaching end-of-life support from the chip manufacturer, which affects your program’s long-term supply chain regardless of what the board vendor says about product availability.

What to ask: What FPGA device is on the board, and what is that device’s product lifecycle status with the chip manufacturer? A board with a chip approaching end-of-life may have a limited support horizon regardless of the board vendor’s policies.

PCIe Interface Generation

The PCIe interface is how the FPGA board moves data to and from the host computer in the chassis. Generation 2 (Gen2) and Generation 3 (Gen3) represent a 2x difference in maximum throughput — Gen2 at approximately 4 GB/s and Gen3 at 8 GB/s for an 8-lane connection. For applications that move large volumes of data continuously, this difference is significant. For applications with moderate data rates it may not matter at all.

What to ask: What is the peak sustained data rate from the FPGA to the host in your application? Engineering should answer with a specific number, not a preference. A board marketed as Gen3 that costs 30% more than a Gen2 alternative is not worth the premium if Gen2 throughput is sufficient for the workload. Also confirm that the chassis slot and host controller support the board’s PCIe generation — a Gen3 board in a Gen2 chassis slot will negotiate down to Gen2.

On-Board DRAM: Capacity and Bandwidth

On-board DRAM serves as a high-speed buffer between the FPGA and the PCIe interface. Its capacity determines how much data can be staged before transfer to the host; its bandwidth determines how fast the FPGA can read and write that buffer. DRAM specifications range from 2 GB on legacy boards to 8 GB on current mid-range boards and up to 20 GB on high-end devices.

What to ask: What is the actual DRAM capacity requirement for this application — not what the board has, but what the application uses in production? Boards with more DRAM cost more. If the application uses 4 GB of buffer capacity, paying for 20 GB represents budget allocated to unused hardware. This is one of the most common sources of over-specification in FPGA board procurement.

High-Speed Serial Interfaces

High-speed serial ports on the board’s front panel connect to instruments, sensors, antennas, or other boards via optical fiber or copper cabling. The number of lanes and speed per lane determine total external connectivity bandwidth. Common configurations range from 4 lanes at 10 Gbps to 48 lanes at 28 Gbps. Higher lane counts and faster line rates drive cost significantly upward — this is typically where boards at similar price points diverge most sharply when you look closely.

What to ask: How many serial lanes does the application actually use in production, and at what line rate? A board sized for 48 lanes when 24 are used carries cost for idle capability. Also confirm which serial protocols the application depends on — Aurora, Interlaken, Serial FPDP, ODI — and verify those protocols are supported on the candidate board before the evaluation goes further.

DSP Slice Count

DSP slices are dedicated signal processing circuits embedded in the FPGA. For signal processing workloads — radar, RF, sonar, communications — DSP slice count is a genuine performance constraint and boards with more DSP slices cost more. For data recording, protocol handling, or routing applications, DSP count is largely irrelevant. The spec appears prominently in datasheets but only matters for a subset of applications.

What to ask: Is DSP slice count a binding constraint for this application? If engineering cannot give you a specific number for how many DSP slices the current design uses and why that number matters, the spec is probably not a meaningful selection criterion for this procurement.

FPGA Intellectual Property (IP) Included With the Board

This is the specification that rarely appears in marketing materials but has the largest impact on total program cost. An FPGA board is not useful until your engineering team has working code — called IP cores — for the board’s interfaces: the PCIe connection to the host, the DRAM controller, and the serial interfaces. These can be purchased from third-party vendors at $10,000 to $50,000 per license, licensed from the FPGA chip manufacturer, or provided by the board vendor as part of the hardware purchase.

Board vendors differ significantly here. Some provide full source code for all major interfaces, tested against their hardware and available for modification. Others provide only hardware documentation and leave IP procurement entirely to the customer. The difference in total program cost between these two approaches can easily exceed the hardware price delta between competing boards.

What to ask: Does the board include working IP for the PCIe interface, DRAM controller, and serial interfaces? Is that IP provided as source code that engineers can inspect and modify, or as locked compiled files? Are there separate licensing fees for any of the included IP? These answers belong in every competitive evaluation alongside the hardware price.

Total Cost of Ownership: The Numbers Beyond the Purchase Price

Hardware price is the number on the quote. Total cost of ownership is the number that matters to the program. For PXIe FPGA boards, three additional cost categories consistently emerge in procurement evaluations — and frequently exceed the hardware purchase price when properly accounted for.

IP Licensing Costs

If the board vendor does not include IP for key interfaces, those licenses must be purchased separately. PCIe DMA IP from reputable third-party vendors runs $15,000 to $40,000 per seat. Interlaken cores — a protocol used in high-speed data applications — run $20,000 to $50,000. These are one-time costs, but they belong in the cost comparison. A board priced $5,000 below a competitor that requires $30,000 in separate IP licensing is not the lower-cost option.

Engineering Integration Time

Bringing a new FPGA board into service takes engineering time. That time varies substantially based on how much IP the board vendor provides and how well it is documented. The range runs roughly two weeks for a well-supported board with comprehensive reference designs to six or more weeks for a board that requires significant bring-up work before development can begin.

At typical senior FPGA engineer billing rates of $150 to $250 per hour, the difference between two weeks and six weeks of integration time represents $24,000 to $80,000 in fully-loaded labor. For programs with constrained schedules, the schedule impact may matter even more than the direct cost.

A practical benchmark: ask each vendor candidate how many weeks a typical customer spends on board bring-up and design integration. Ask for a reference customer you can call. The honest answers — and the willingness to give them — tell you as much as the technical specifications.

Ongoing Support and Maintenance Costs

Large PXIe vendors offer tiered support contracts running $5,000 to $15,000 per year per system. Smaller specialized vendors often provide direct engineer-to-engineer access without formal contracts, which can deliver faster resolution for technical issues. The meaningful question is not whether a support contract exists, but how quickly a specific technical question reaches someone with hardware-level knowledge of the board. Tiered help desk routing and direct engineering access are different categories of support, regardless of what either is called on a contract.

Vendor Evaluation: Six Questions That Matter

Hardware specifications are verifiable on paper. Vendor quality and program risk are harder to assess from a datasheet. These questions structure the vendor evaluation beyond the hardware comparison.

1. What is the product’s longevity outlook?

FPGA boards in defense and measurement programs routinely remain in service for five to ten years. Ask each vendor about their product revision history, typical product lifecycle, and commitment to backward compatibility when new revisions are released. A vendor who has shipped the same board family for several years with incremental improvements is a different risk profile than one with a history of frequent discontinuations or major architectural changes between revisions.

2. Who actually answers when there is a problem?

Large vendors route support through tiered help desks. Specialized vendors often provide direct access to the engineers who designed the board. A board-level hardware issue can take days to resolve through a help desk and hours with a direct engineering contact. Ask each vendor specifically: who responds to a priority support request and how do you reach them?

3. Where is the hardware manufactured and what is the supply chain?

For US defense programs with domestic content requirements, manufacturing location is a compliance question. For any program, supply chain resilience is a risk question. A vendor with a single manufacturing source and no component inventory buffer carries higher supply chain risk than one with stocked components and multiple fabrication options. Ask about standard lead times and what lead times looked like during the most recent period of component scarcity.

4. What does the warranty actually cover?

Standard hardware warranties in this market run one year. Understand exactly what is covered, what the repair or replacement process looks like, and what the turnaround time is. For programs where system downtime has direct cost implications, warranty terms and post-warranty support options belong in the cost comparison.

5. Are there customer references in similar applications?

A vendor with deployed hardware in applications similar to yours is a lower-risk choice than one whose reference base does not map to your use case. Ask for references and call them. Questions worth asking: how was board bring-up? How responsive was vendor support when problems arose? Would you buy from them again for a new program?

6. What technology partnerships does the vendor hold?

Formal partnerships with FPGA chip manufacturers — AMD in particular — indicate engineering depth and access to technical resources that benefit customers. Tier-1 partnerships provide access to reference designs, early product roadmap visibility, and escalation paths that translate into better IP delivered with the board and faster resolution of chip-level issues.

The Vendor Landscape

The PXIe FPGA board market is specialized. The primary vendors serving defense, aerospace, test and measurement, and scientific research applications are Conduant Corporation, National Instruments, Abaco Systems, and Mercury Systems. Each has a distinct positioning.

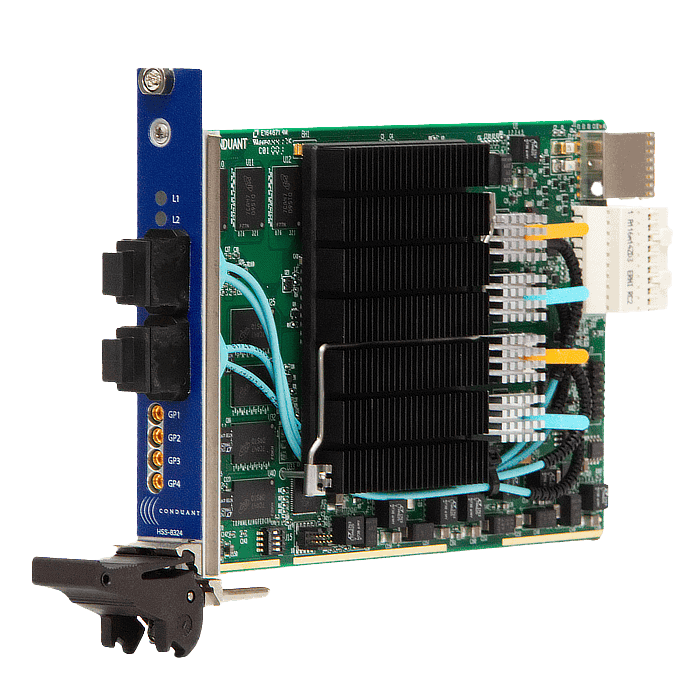

Conduant Corporation focuses on high-speed optical FPGA boards and PXI storage for data-intensive applications: radar, electronic warfare, SIGINT, VLBI data capture, and high-speed recording. Conduant is an AMD Adaptive Computing Select Partner and Keysight Solutions Partner. Boards use current-generation AMD Kintex UltraScale FPGAs and ship with source-level IP for PCIe, DRAM, and optical serial interfaces. Engineering support goes directly to the engineers who designed the board.

National Instruments (NI, now part of Emerson) is the largest vendor in the PXI ecosystem. NI’s strength is breadth — a complete hardware and software platform covering chassis, controllers, FPGA boards, data acquisition, signal generators, and analysis software. The LabVIEW FPGA development environment lowers the barrier to FPGA development for teams without deep VHDL experience. The tradeoff is cost: NI hardware carries a significant price premium over comparable hardware from specialized vendors, and the software stack creates platform lock-in. Support is large but tiered.

Abaco Systems targets defense and aerospace with ruggedized form factors — VPX and VME alongside PXIe. The right consideration when deployed environment specifications (temperature range, vibration, shock) exceed what standard commercial hardware supports.

Mercury Systems is a defense-focused electronics company that acquired Pentek and now covers a broad portfolio spanning signal processing, compute, data management, display, and secure processing. Mercury serves primarily aerospace and defense programs requiring ruggedized hardware with strong security credentials — NSA Type-1 encryption, anti-tamper technology, and radiation-tolerant variants for space applications. A relevant consideration when program requirements extend into those areas.

Managing Program Risk Through the Procurement Process

Hardware procurement for long-duration programs introduces risk categories that warrant explicit management independent of which vendor is selected.

Single-Vendor Dependency

A program that can only be served by a single hardware vendor has limited leverage at renewal and no fallback if that vendor has supply problems or discontinues the product. Building a qualified alternative source into the procurement strategy — even if the primary vendor remains preferred — provides negotiating position and supply chain resilience. The PXI Express standard exists precisely to support this: any compliant board from any vendor should be physically interchangeable, even if software integration requires engineering work at the time of transition.

Component End-of-Life

FPGA boards are subject to component obsolescence driven by the chip manufacturers, not the board vendor. When a critical component — the FPGA device, DRAM, or a key interface chip — reaches end-of-life, the board vendor faces a redesign or a discontinuation decision. Ask each vendor what their projected availability horizon is for the specific board and what their obsolescence management policy looks like in practice. Vendors who proactively notify customers of end-of-life timelines and stock longevity inventory are meaningfully lower risk for programs spanning five or more years.

FPGA Design Portability

The FPGA design running on the board is a program asset with its own portability profile. Designs written in standard VHDL or Verilog can be migrated to a different board with engineering work proportional to the interface differences. Designs written in vendor-specific graphical environments are more tightly coupled to a particular hardware platform. Programs that have not yet committed to a development environment should factor portability into the selection. Programs already invested in a specific development environment should account for migration cost explicitly in any alternative hardware evaluation.

Lead Time

FPGA boards have experienced extended lead times during periods of semiconductor supply constraint. Ask each vendor their current lead time, what it was during the most recent supply disruption, and what stocking or priority fulfillment options are available. Programs with fixed delivery schedules should treat lead time as a hard procurement constraint, not an assumption.

A Procurement Checklist

These are the questions that consistently surface after a procurement decision is made. Work through them before, not after.

Technical Validation

- Engineering has confirmed actual FPGA resource utilization on existing or comparable hardware — not just the spec sheet

- Serial lane count and line rate requirements documented based on application needs, not board maximums

- DRAM capacity and bandwidth requirements confirmed against actual application buffering strategy

- Required serial protocols confirmed supported on candidate board before evaluation continues

- Candidate board is on the vendor’s validated chassis list for the chassis in the system

- PCIe generation matches chassis slot bandwidth capability

Total Cost of Ownership

- IP licensing costs identified and included in cost comparison

- Engineering integration and porting effort estimated and included in cost comparison

- Annual support contract cost included in multi-year program cost projection

- Lead time confirmed against program schedule

Vendor Evaluation

- At least one customer reference called — in a similar application if possible

- Support escalation path confirmed — who responds to a priority technical request and how

- Product lifecycle and obsolescence management policy reviewed

- Manufacturing location confirmed against any domestic content requirements

- Warranty terms and post-warranty support options documented

Program Risk

- Single-vendor dependency risk assessed; qualified alternative source identified if program duration warrants it

- FPGA design portability assessed — standard VHDL/Verilog vs vendor-specific development environment

- Component end-of-life horizon confirmed relative to program duration

- Lead time risk addressed explicitly for fixed-schedule programs

PXIe FPGA board procurement is a decision where the hardware price is often the least significant variable once total cost of ownership, IP, and program risk are fully accounted for. Programs that evaluate all of these factors together — not just the spec sheet and the purchase price — tend to make decisions they do not need to revisit.

If your program is procuring or evaluating a PXIe FPGA board, Conduant’s engineering team is available for consultation. Bring your requirements and expect a direct answer on whether our hardware fits your application. View Conduant PXIe FPGA development boards or explore PXI data storage options.