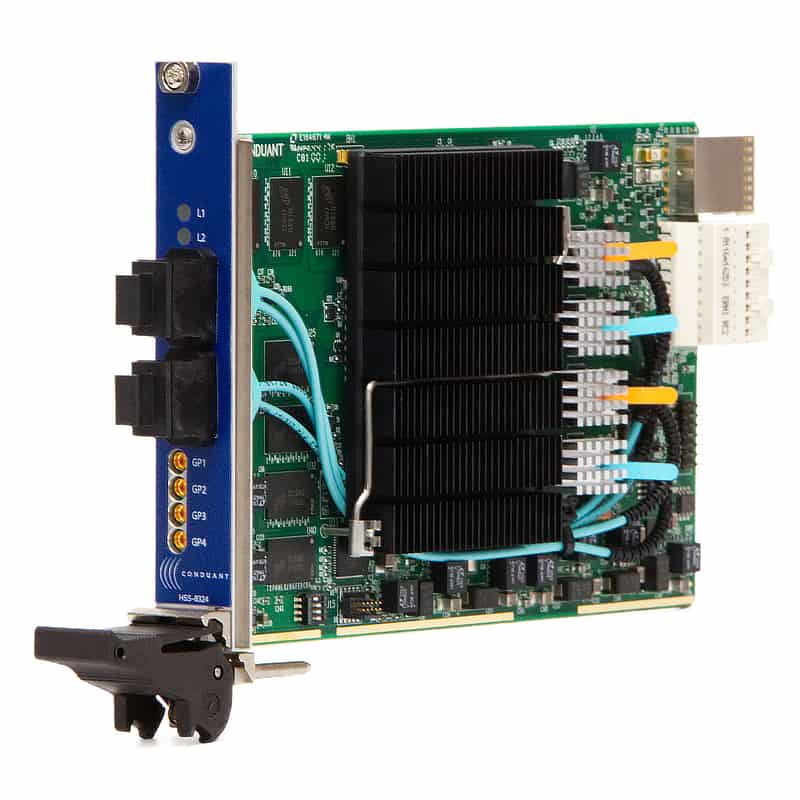

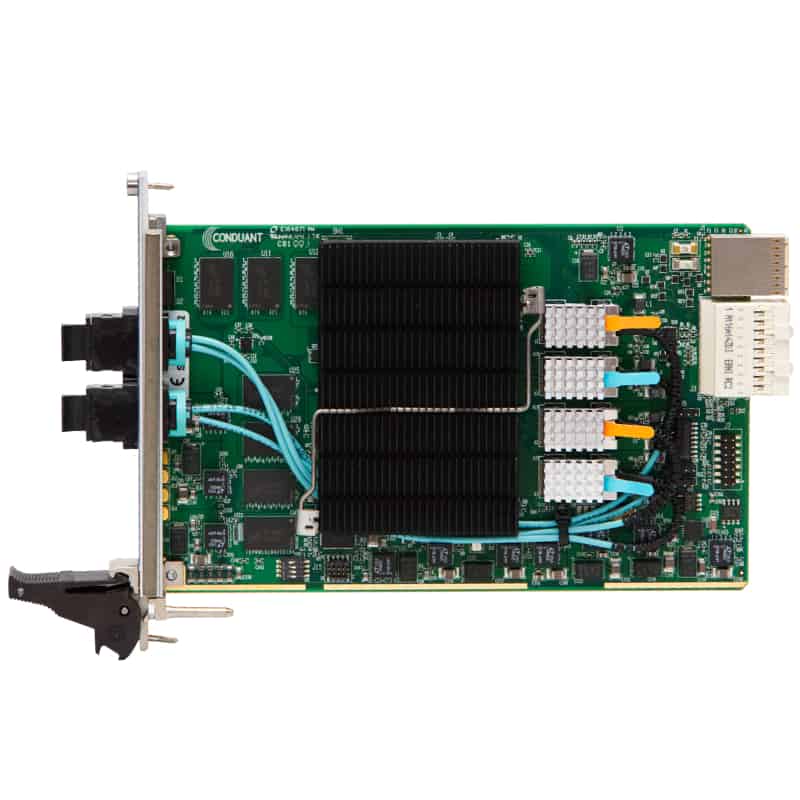

The Conduant PXIe-8324-DSP FPGA board provides a user programmable hardware platform that is able to sustain full-duplex high-bandwidth transfers through its 8-lane Gen3 PXI Express (PXIe) interface and its two 12-lane HSS interfaces while performing complex calculations. The PXIe interface provides a theoretical maximum throughput of 8 GBps (simultaneous in and out) while each HSS port (12 lanes up to 16 Gbps per lane) supports a full duplex transfer at theoretical rates over 190 Gbps.

The board includes both 8 GiB of high-speed DDR3 SDRAM and 8 MiB of QDR II+ SRAM. At the center of the design is an AMD (Xilinx) Kintex Ultrascale FPGA which interconnects all ports and other devices while supplying additional resources within the FPGA. The FPGAs available on this board contain a high count of DSP elements which uniquely suits this board for signal processing.

With up to 24 HSS lanes and 4 MMCX coaxial connections available, the board can be used for numerous applications that require high speed data connectivity with advanced DSP functionality. Note that each HSS lane can operate independently or in a bonded configuration if supported by the protocol being used. Popular HSS protocols that can be implemented include but are not restricted to Aurora, Interlaken, Serial FPDP, and ODI (Optical Data Interface).

At power-on, the FPGA is quickly configured with the user program by the SPI x4 serial flash memory device. This provides the fast wake-up required for PCI Express. The user content can be encrypted with a key that is programmed in the FPGA in non-volatile EFUSEs or can be preserved in volatile memory so long as the on-board battery is not removed. This feature makes this product particularly attractive for applications in which protecting the FPGA intellectual property from cloning or reverse engineering is important.

To improve clocking flexibility, the board includes a Skyworks clock synthesis part that supports both integer and fractional divides. While the provided VHDL project uses the internal I2C bus to initialize these clocks at power-up for the self test function, the user can access the I2C bus if different frequencies are needed.